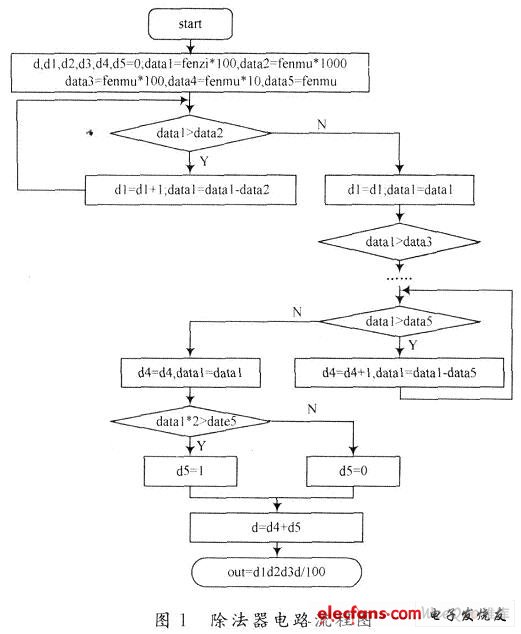

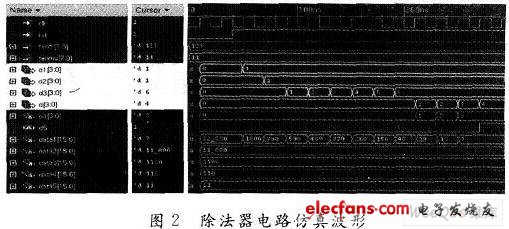

0 Preface The divider is a basic module in the field of electronic technology and is widely used in electronic circuit design. At present, the methods for implementing the divider have two methods: hardware implementation and software implementation. The hardware implementation method is mainly at the cost of hardware consumption, so that it has the characteristics of fast implementation. There are many researches on the implementation of the divider by hardware methods, such as using the microprocessor to implement fast multiplication and division operations, FPGA to implement binary division operations, analog dividers, etc.; and the divider algorithm implemented by software can greatly improve the operating frequency of the device. And the flexibility of design can improve the design performance as a whole, and the design of efficient and practical algorithms is the key to the divider. Therefore, the algorithm research of the divider has become a hot topic. At present, the software mainly implements the division operation by the subtraction algorithm, taking the dividend as the subtraction and the divisor as the subtraction, and subtracting until the subtraction is less than the subtraction, and the number of times the record can be subtracted is the integer part of the quotient. . Multiply the obtained remainder by 10 as the subtracted number, the divisor as the subtraction, subtraction, the difference is re-inputted by the subtraction, and the subtraction is repeated until the subtraction is less than the subtraction, and the number of times the record can be subtracted is obtained. The decile value. In this way, you can get the percentile value of the quotient, the value of the thousandth digit, ..., which one to be precise, which one to do. The disadvantage of this method is that the speed is slow, and the accuracy of the last bit is not high. In order to overcome the above shortcomings, an algorithm is designed here to improve the accuracy and processing speed of the divider operation in software. 1 Design method For any given two integers fenzi and fenmu, let fenzi be the dividend and fenmu be the divisor. In order to obtain the decimal result of dividing the two numbers, the design is mainly realized by the following algorithm. If the n significant digits after the decimal point are to be reserved, first multiply fenzi by the nth power of 10 and assign it to the register variable dataO; Multiply fenmu by 10 (n+m), (n+m-1), (n+m-2),...,1,0 powers respectively assigned to (n+m+1) different variables Data(n+m+1),data(n+m),...,datal, where m is the difference between the number of digits of fenzi and fenmu (w is positive if fenzi has more digits than fenmu, otherwise negative) First, find the value of the highest bit of the quotient. If dataO is greater than data(n+m+1), the counter is automatically incremented by 1, and then the difference between dataO and data(n+m+1) is assigned to data0. Decrease until the value of data0 is less than data(n+m+1). At this time, the counter value is the highest value; by continuing in the same way, the value on each bit can be obtained. Rounding up the last digit, when subtracting dataO 2 Simulation results and analysis The above flow chart is programmed in Verilog description language, and simulated under Ca-dence's NC-Verilog simulator. The values ​​of input Ienzi and fenmu are 128 and 11, respectively, and the simulation waveform is shown in Fig. 2. As can be seen from the waveform of Figure 2, the output is 1 164, the division is accurate to the percentile, and the previous left shift is 2 bits, the final value is 11.64, and the actual value is 11.636 36... ..., the results obtained after rounding are done correctly. From the simulation time, for the same numerical input, the design uses only 12 pulses, while the normal divider requires at least 20 pulses (128/11=11, 7, 70/11=*, 40/11=3) The remaining 7,1l+6+3=20), compared to the division algorithm of this design has great advantages. However, for the division of two numbers with a large number of digits, the speed advantage of this design is more obvious. The running time of each bit of this design will not exceed 9 clock pulses, so the total pulse of z-bit calculation is performed. It will not exceed 9n, and the traditional divide operation requires multiple clock pulses, which is typically several times the design clock pulse. The algorithm is also suitable for decimal operations. As long as the decimal is converted to an integer and then the same processing is performed, accurate results can be obtained. 3 Conclusion Through the improvement of the divider algorithm, the data is processed by rounding, so that the accuracy of the obtained results is further improved. The shift and loop subtraction are used to realize the high-speed operation of the data, and the calculation accuracy can be arbitrarily set. . Using this method to design the divider in software has a positive effect on the speed and accuracy. Shenzhen Isource lighting Co., Ltd , https://www.isourceled.com