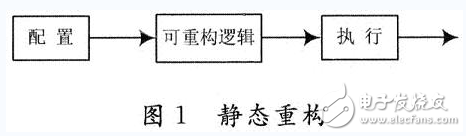

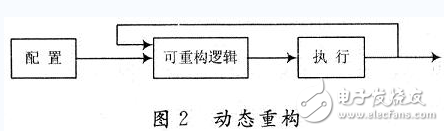

As digital logic systems become more complex, the chips in monolithic systems are evolving toward ultra-large scale and high density. In large-scale digital systems, the overall system size is built by combining various logical function modules. However, regardless of whether it's a sequential logic system, a combinational logic system, or a hybrid system, each functional module doesn't operate continuously over time. Instead, it is activated or operated cyclically based on the system’s overall requirements. Moreover, as the scale of digital logic systems increases, under the same speed conditions, the average utilization rate of functional modules tends to decrease over certain time intervals. Therefore, system design must shift from merely pursuing large-scale and high-density solutions to focusing on improving resource utilization and achieving larger-scale logic designs with limited resources. Reconfigurable computing technology offers both hardware efficiency and software programmability, combining the advantages of microprocessors and ASICs while allowing flexibility in both spatial and temporal dimensions. Reconfigurability refers to the ability of an electronic system to dynamically change its circuit structure during operation. This is typically achieved through reconfiguration or partial reconfiguration of programmable logic devices within the system. With reconfigurable technology, a system can combine the benefits of both software and hardware implementations using only a minimal amount of additional hardware resources. Based on the method of reconfiguration, system reconfiguration can be categorized into static system reconfiguration (Static Reconfiguration) and dynamic system reconfiguration (Dynamic Reconfiguration). 1.2.1 Static System Reconfiguration Static system reconfiguration involves loading the logic function of the target system before execution, as shown in Figure 1. The FPGA function is re-downloaded based on different target system data stored in memory, controlled by external logic, thus enabling changes in the chip’s logic function. 1.2.2 Dynamic System Reconfiguration Dynamic system reconfiguration allows for real-time configuration of the system during operation, as illustrated in Figure 2. For digital logic systems with time-varying behavior, timing logic is not generated by calling different regions or resources on the chip, but rather through the dynamic restructuring of local or global logic within FPGAs that have dedicated cache logic resources. The FPGA of a dynamic system has Cache Logic. Under the control of external logic, the chip logic is quickly modified either globally or locally using the cache logic. This accelerates the dynamic configuration of the system through resource configuration with control relocation and routing. In terms of area, dynamic reconfiguration can be classified into global and local reconfiguration. (1) Global Reconfiguration: This involves completely reconfiguring an FPGA device or system. During the configuration process, intermediate results must be stored in an external storage area until the new configuration is fully downloaded. The circuits before and after reconfiguration are independent and not related. (2) Local Reconfiguration: This allows partial reconfiguration of the device or system while keeping the rest of the logic unaffected. Local reconfiguration significantly reduces the scope and number of elements involved, thereby greatly decreasing the reconfiguration time. In the past, FPGAs commonly used for dynamic reconfiguration research included Xilinx’s XC6200 series and Atmel’s AT6000 series. These were SRAM-based, allowing individual units of SRAM to be accessed separately, enabling local reconfiguration. Their functions do not interfere with each other, giving them the capability for local reconfiguration. While this approach offers significant advantages, it also increases hardware size and power consumption. To achieve full real-time reconfiguration, FPGAs with dynamic local reconfiguration capabilities, such as Xilinx’s Virtex-4 series, are required. The key feature of FPGA-based local dynamic reconfigurable technology is the ability to decompose the entire system into different functional or timing-based components and perform local dynamic reconfiguration according to actual needs. This allows the realization of a large-scale timing system with fewer hardware resources. Figure 3 shows a typical example of FPGA-based local dynamic reconfiguration. As seen in the figure, under the control of external logic, the chip’s logic can be dynamically reconfigured in real time. The system is restructured by controlling the layout and routing of resources. To effectively implement real-time dynamic reconfiguration in an FPGA, the device must meet the following structural requirements: (1) Not only should it be reprogrammable, but it must also support dynamic reconfiguration of system resources without disrupting the global or local logic operations within the device. Traditional FPGAs often store configuration data in an external serial EPROM, which has several disadvantages: the entire FPGA must be stopped before reconfiguration, only the whole device can be reconfigured, and the internal state cannot be saved during the process. New dynamic reconfigurable FPGAs do not require a reset signal before reconfiguration. Instead, they disable the clock of a portion of the logic circuit, reconfigure the logic, and then restore the clock signal. (2) The internal configuration information of the FPGA must be symmetrical. At any time, any basic logic function can be configured at any position on the device, and complex functions can be realized through simple model combinations. The demonstration system consists of several hardware components, each responsible for specific functions. These include the main processing unit, memory modules, I/O interfaces, and a reconfigurable logic block. Each part plays a crucial role in enabling dynamic reconfiguration and testing the performance of the system under varying configurations.

China Top Laptop Stand Ergonomic, Ergonomic Flexible Laptop Stand, Adjustable Laptop Computer Stand Manufacture in Shenzhen. Shenzhen Chengrong Technology Co.ltd is a high-quality enterprise specializing in metal stamping and CNC production for 12 years. The company mainly aims at the R&D, production and sales of Notebook Laptop Stands and Mobile Phone Stands. From the mold design and processing to machining and product surface oxidation, spraying treatment etc ,integration can fully meet the various processing needs of customers. Have a complete and scientific quality management system, strength and product quality are recognized and trusted by the industry, to meet changing economic and social needs .

Laptop Stand Ergonomic,Ergonomic Flexible Laptop Stand,Adjustable Laptop Computer Stand,Desktop Foldable Aluminum Laptop Stand Shenzhen ChengRong Technology Co.,Ltd. , https://www.laptopstandsupplier.com