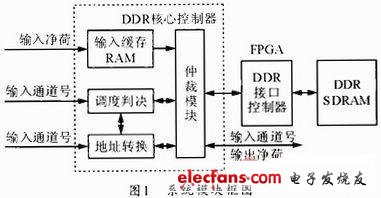

In this paper, DDR SDRAM is used as a storage unit. Without changing the system clock, the clock double-edge is used to transmit data, and the transmission bandwidth of the chip with the same frequency is doubled on the basis of SDRAM, which satisfies the needs of high-bandwidth cache. . 1 Introduction to DDR memory DDR memory is double data rate synchronous dynamic random access memory. It is the same as the early single data rate synchronous dynamic random access memory. The internal storage unit uses capacitor charging to save data, so the capacitor must be constantly charged to maintain data. This is called "Refresh". The data bus of SDRAM accesses data on the rising edge of each clock, while DDR SDRAM accesses data on the rising and falling edges of each clock, so that the data bus bandwidth is the same as the data bus width and clock frequency. Doubled the promotion. 2 System design The design uses Xitanx's Sptan3a-dsp 1800a as the main controller and Micron's MT64V32X16 chip as the storage medium, with a maximum storage capacity of 512M. The logic part of this system is composed of arbitration module, input buffer module, scheduling decision module, address conversion module and DDR interface control module. The structural block diagram is shown in Figure 1. The arbitration module in the core controller generates corresponding control commands. Complete the initialization and reset after power-on, and in the process of system operation, according to the work priority, issue refresh instructions, write operation instructions and read operation instructions; the DDR interface control module implements the core controller instructions according to the basic timing of DDR chip operation For information transmission of physical chips; Nanyu DDR chips have non-real-time operating characteristics, and must use the internal input cache RAM for basic real-time data buffering; and the address conversion module and scheduling decision module cooperate with the internal input cache RAM to complete the DDR chip Mapping of internal storage space. 3 DDR core controller design DDR memory is a high-speed memory chip with relatively complex instructions. It must be initialized after power-on to perform other operations; it does not support single-cycle read and write operations, and only supports burst read and write operations with periods of 2, 4, and 8. In addition, due to its capacitance characteristics, DDR chips are unstable in data storage, and need to be refreshed within a certain period of time to ensure that data will not be lost. Therefore, there are dozens of instructions during the DDR operation. But in this design, the DDR interface controller uses the DDR IP provided by Xilinx, so that the arbitration module in the core controller only needs to use 4 instructions such as idle, initialization, read operation and write operation to complete the DDR-SDRAM. Operation, greatly reducing the design difficulty. Because the design goal is to eliminate the jitter from the network to the IP data, and ultimately to distribute the IP data to 512 channels, which greatly exceeds the previous design's use of DDR, so this article proposes the design shown in Figure 1 here, you can complete Design and application of DDR memory to high-speed large-capacity multi-channel: (1) Input cache module The input buffer consists of a RAM plus external logic circuits, which buffers the TS packet payload that has been input but has not had time to write to the DDR. After the arbitration module sends a signal to allow writing, the data packet in the input buffer is passed to the arbitration module, and the corresponding storage space is released. According to the working mode of DDR and the characteristics of DVB-C, the data transmission of the input buffer takes TS packets as a unit to realize continuous burst transmission of 192 bytes. (2) Scheduling decision module The scheduling decision module receives the read request queue information and implements the decision to dispatch the FIFO with the largest amount of data in the same bank out of the queue when reading data. This module saves the current number of data packets in each channel FIFO. (3) Address conversion module The address conversion module is responsible for mapping the channel number and the internal storage space of the DDR SDRAM chip. The variables saved in this module include the block start address, block end address, FIFO head offset and FIFO tail offset of each channel in DDR SDRAM. (4) Arbitration module The arbitration module generates corresponding control commands, and issues idle commands, initialization commands, write operation commands, and read operation commands according to the work priority.

This portable

Bluetooth Speaker is a portable, waterproof and good sound Portable Speaker systems. Small size

but hold a [Big world" in it, it combines all the standard functions of traditional speakers. With its rechargeable high-volume

Li-ion battery, it can play long time. It can be connected with your

phone by Bluetooth, and it also built-in USB port, you can play the music you like

any time. It is prefect for schools, parties, outdoor activities and

presentations, it is your best choice for portable

wireless mic system.

Portable Bluetooth Speaker,Trolley Bluetooth Speaker,Portable Speaker,Portable Mini Speaker Shenzhen New Wonderful Technology Co., Ltd. , https://www.sznewwonderful.com