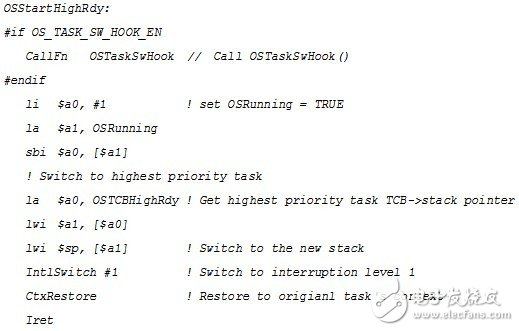

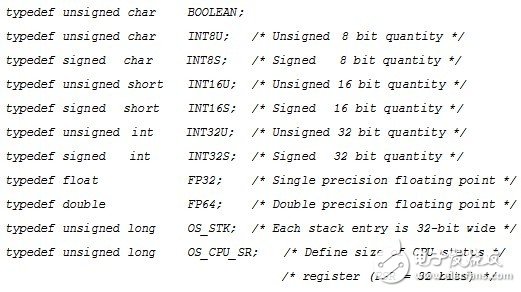

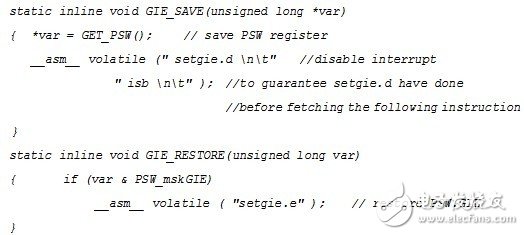

μC/OS-II is an open, real-time multitasking operating system with open code and tailorability. The kernel achieves high efficiency and high real-time performance by implementing preemptive task scheduling algorithms and multi-task communication. In addition, it has a very small footprint (minimum cut to 2KB) and is highly portable, so it is widely used in microprocessors and microcontrollers. Andes is the first original 32-bit microprocessor IP and system chip platform design company in Asia, and launched the AndesCoreTM N10 series N1033A-S with a wide range of embedded real-time operating systems μC/OS-II. And related hardware and software development resources, effectively helping customers reduce existing costs, improve system performance, reduce system power consumption, and shorten product development time-to-market. This article describes how to port μC/OS-II to the AndesCoreTM N1033A-S processor. 1. Development environment and processor introduction 1.1 Software/Hardware Development Environment The software environment used in this migration process is AndeSight? V1.4 integrated development kit, which is the latest launch of Jingxin Technology for various AndesCore? Software integrated development environment, including compilers, debuggers, parsers, and powerful ESL tools. The hardware platform uses Crystal's FPGA evaluation board ADP-XC5. The evaluation board uses AndesCore? The N1033A-S acts as a processor core and has a rich set of on-chip resources. Introduction to AndesCoreTM N1033A-S The AndesCoreTM N10 series N1033A-S is a Haval-structured 32-bit RISC processor core with a 5-stage pipeline and Dynamic branch predicTIon architecture. The N1033A-S has added the latest AndeStarTM V2 instruction set to push CPU performance above 1.66 DMIPS/Mhz. It also implements the complete Audio instruction set to achieve the goal of fully integrating CPU and DSP functions. The N1033A-S also supports vectored interrupt mode and 2D direct memory access (DMA) for added real-time signal processing. 2. Portability analysis of μC/OS-II on N1033A-S μC/OS-II is highly portable and has been ported to nearly 40 processor systems, ranging from 8-bit to 64-bit CPUs (including DSPs). The normal operation of μC/OS-II requires the processor platform to meet the following requirements: 1) the processor's C compiler can generate reentrant code; 2) the C language can be used to turn interrupts on and off; 3) the processor supports interrupts, And can generate a timed interrupt; 4) the processor supports a hardware stack capable of holding a certain amount of data; 5) the processor has instructions to read and store the stack pointer and other CPU registers onto the stack or memory. AndesCore? The N1033A-S provides 32 general-purpose registers internally, of which R31 is used to make a dedicated stack pointer. The 32 address lines can access up to 4GB of memory cells, so there is no limit to stack space theory as long as the system RAM space allows. AndeStar from the N1033A-S processor? The V2 instruction set contains a rich and very efficient instruction to operate on the stack. For example, the instruction SMW (store mulTIple word) can store the values ​​of multiple registers onto the stack with only one instruction and update the stack pointer position at the same time, and can also handle the access of address non-aligned words. The N1033A-S supports interrupts and can generate timer interrupts. The PSW (Processor Status Word) register in the processor contains a global interrupt disable bit, GIE, which can be turned on and off. In addition, AndeSight? The built-in compiler in the integrated development environment can generate reentrant code and support inline assembly. The C environment can be arbitrarily switched and interrupted. In summary, μC/OS-II can be fully ported to the N1033A-S. 3. Migration steps In order to facilitate porting, most of the μC/OS-II code is written in C language. Users only need to write some processor-related code in C language and assembly language to implement porting. The contents of this part of the work include: a header file os_cpu.h that completes the basic settings, a processor-related assembly file os_cpu_a.S, and an operating system-related C code file os_cpu_c.c. 3.1 Complete basic configuration and definition in os_cpu.h 3.1.1. Defining processor-related data types To ensure portability, μC/OS-II does not directly use the definitions of data types such as short, int, and long in C because different processors have different word lengths. For 32-bit processors such as the N1033A-S, the data type definitions are implemented as follows: 3.1.2. Defining interrupt disable/allow macros As a real-time kernel, μC/OS-II needs to disable the interrupt and then access the critical section of the code, and re-enable the interrupt after the access is completed. μC/OS-II defines two macros to disable and allow interrupts: OS_ENTER_CRITICAL() and OS_EXIT_CRITICAL(). The implementation code on the N1033A-S processor is as follows The implementation of GIE_SAVE and GIE_RESTORE is as follows: The interrupt prohibition time is one of the important indicators for judging the real-time nature of the system. Whether the interrupt disable time can be minimized depends not only on the design of the operating system, but also on the processor structure and the quality of the code generated by the compiler. As seen from the implementation code above, since the Andes processor provides two sets of commands that directly control the interrupts of setgie.d and setgie.e, the entire process of disabling/allowing interrupts is only 3/2 of the machine code generated by the compiler. Minimizes the interrupt disable time. 3.1.3. Defining the stack growth direction μC/OS-II uses the structural constant OS_STK_GROWTH to specify how the stack grows. Setting it to 0 means that the stack grows from bottom to top, and setting it to 1 means growing from top to bottom. Here we define the latter, that is, the growth direction of the stack is decremented from the memory high address to the low address direction and the stack pointer always points to the top data: 3.1.4. Defining the OS_TASK_SW() Macro OS_TASK_SW() is a macro that is called when μC/OS-II switches from a low priority task to a highest priority task. Task switching simply saves the processor registers to the stack of tasks that will be suspended and restores higher priority tasks from the stack. There are two ways to define this macro, use a soft interrupt to point the interrupt vector to the OSCtxSW() function, or directly call the OSCtxSW() function, where we use the latter (the implementation of the OSCtxSW() function will be described later): 3.2 processor related parts assembly implementation The migration of μC/OS-II requires the user to write three basic assembly language functions: OSStartHighRdy(), OSCtxSw(), OSIntCtxSw(). They share some code and write them in the same assembly file os_cpu_a.S for readability. 3.2.1 OSStartHighRdy(): Runs the highest priority ready task. The OSStartHighRdy() function is responsible for obtaining the stack pointer SP of the task from the TCB control block of the highest priority task after the OSStart() multitasking is started, and recovering the CPU scene through the SP to start the highest priority task execution. In addition OSStartHighRdy() must also set OSRunning to TRUE before the highest priority task is restored and after calling OSTaskSwHook(). The implementation code is as follows:

New high

mast light are driverless designed. The LED high mast lights are utilizing

PHILIPS LUXEON 3030 2D luminous source, providing excellent lumen output – up

to 150 LPW, long-lasting stability and splendid sight. Easy

assemble/disassemble, neat wiring & connection, up to 115 LPW luminous

efficiency, IP66 and IK10 Rated, 90%+ driver efficiency, over than 75,000 hours

operation life and 5 years warranty. They are high intensity, durable lights

that are typically used to illuminate large areas, flag poles, building

facades, and many other applications.

High Mast Lighting,Stadium High Mast Lighting,Football Field High Mast Light,Aluminum Die Casting High Mast Lighting Shenzhen Ri Yue Guang Hua Technology Co., Ltd. , https://www.ledlightinside.com

![]()

![]()

![]()