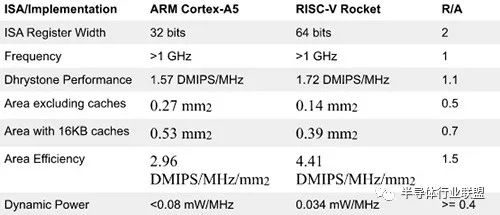

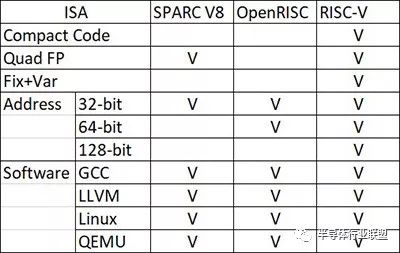

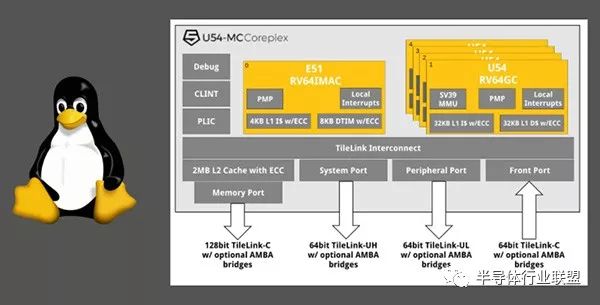

In February 2018, the American new entrepreneur SiFive (Figure 1) released the technical details of the FreedomU500 chip. In the same month, the French new chip maker GreenWave also released the GAP8 chip, plus follow-up related news, such as Taiwan's Andes Technology (Andes) launched AndeSatrV5 silicon Intellectual Property (IP) and Intel (Intel) invested in SiFive, etc., so that RISC-V instruction set architecture (Instruction Set Architecture, ISA) has gradually attracted the attention of the industry. Figure 1 SiFive co-founder and chief technology officer Yunsup Lee holds a RISC-V prototype chip in the Par laboratory of Berkeley in 2013. Before the above news, a number of major technology manufacturers have indicated that they support RISC-V, including Samsung (Samsung), NVIDIA, and Western Digital (WD). The industry has sporadic attention to this, but as the chips get closer Commercial use, attention began to increase. What is the RISC-V instruction set architecture? Why is it gradually gaining support from major technology companies and new entrepreneurs? This article will analyze and discuss this below. Intel/Amou is a dedicated instruction set architecture RISC-V is an open source code instruction set architecture. In fact, it was only called the instruction set (InstructionSet) for a long time in the industry, but it may be added to the architecture (Architecture, InstructionSet) in order to make up three letters that can be abbreviated. A) One word. The instruction set refers to a set of instructions for a combination of language (the most basic primitive language on a chip). A set of instructions is composed of as few as dozens and hundreds of instructions. If a microcontroller , The micro-processing chip can execute this set of instructions, and the other one can also support the execution of the same set of instructions. In this way, in principle, the software (software is composed of instructions) does not need any rewriting, and can be freely used in two Inter-chip replacement application. In the same way, chip manufacturers launch a new generation of better-performing chips, usually adopting the same instruction set as the previous generation, or fully compatible but adding new instructions to ensure that many developed software do not need to be rewritten and can be compared. The capacity execution guarantees the customer's past software development investment and purchase investment, and the execution is faster. At present, most of the chips on the market adopt the instruction set architecture of Intel or Arm. Intel's instruction set architecture is generally called x86 (in the past, it was used in the series of chips ending with 86, such as 8086, 80286, 80386, and 80486). ), IA (Intel Architecture), IA-32 (32-bit from 1982 to 2003), EM64T (ExtendedMemory64Technology) or AMD64/x86-64/x64 (64-bit version is led by AMD), etc. An Mou is directly referred to as the Arm instruction set architecture. The instruction set architectures of Intel and Arm are proprietary and proprietary architectures designed by the industry, and can only be used with a fee. Intel's ISA must be obtained by purchasing CPU chips sold by the company; Arm's ISA is sold indirectly, and chip vendors want to use it. To execute its ISA, a one-time technology licensing fee must be paid first, and then a royalty fee will be collected by Arm for each chip produced. Intel’s x86ISA chips are overwhelmingly dominant in PCs, workstations, servers, supercomputers and other fields. Therefore, the price has been high for a long time, and system vendors and end consumers must bear the costs. Although a few chip vendors can also produce and sell x86ISA Chips, but the price performance ratio or supply is not as good as Intel, and there are many restrictions. For example, AMD can use x86ISA, but if the company is later acquired, the right to use the x86ISA patent must be discussed again, or other chip vendors may also Produces x86 compatible chips, but must pay an annual royalty fee to IBM to avoid possible litigation by Intel. As for Arm, Arm's ISA has an overwhelming market share in the field of mobile device chips, and continues to expand to various embedded applications. Arm provides licenses in the form of soft and hard cores. Soft cores can obtain instruction set architecture, while hard cores can only obtain wafer circuits that have been implemented using a certain semiconductor process technology. Arm tends to provide hard-core licenses to avoid leakage of core technology, but some heavyweight players have obtained soft-core licenses, such as Qualcomm, and it is generally speculated that Apple and Samsung are also among them. According to GreenWave's interview, it takes at least US$15 million to obtain a soft-core license, and it is only for time-based use. The license must be re-negotiated when it expires. Since once a lot of chips or software adopt a certain ISA, the technical ecology of the ISA becomes more and more complete and strong, the owner of the ISA architecture will be regarded as easy to enjoy the profits in the future, chip vendors (chip vendors without ISA independence) , System vendors, and end users will all suffer. For this reason, in 2010, academia and industry jointly initiated the establishment of the RISC-V Foundation, and continued to promote an ISA with open technical details and free technical authorization. Open and free licenses. From the perspective of another key component of the information technology industry, the operating system has already developed in this mode. The early operating system was developed by computer system vendors with their own hardware and shipped together with hardware sales, such as large-scale IBM Host. Later, IBM eagerly entered the PC market, adopted Microsoft's operating system, and then opened a pure software commercial licensing model for operating systems across different system vendors. However, the operating system code was still exclusively owned by Microsoft. Later, Linux emerged and programs The code is open and freely authorized to use. Corresponding to the development process of ISA, Intel’s ISA is shipped with its own chips, and Arm is a cross-chip vendor authorized its ISA, but they are all exclusive and closed and chargeable, while RISC-V tries to imitate Linux and adopts open and free Way of development. RISC-V adopts BSD authorization Although RISC-V adopts an open and free route, it is different from other silicon intellectual property projects with open source code in some places. For example, it has its own hardware description language (HDL), namely Chisel (ConstructingHardwareInaScalaEmbeddedLanguage), which can be understood from the full writing It is developed based on the Scala language, and Chisel also adopts an open source policy. Compared with the commonly used hardware description language, Verilog is used, but there are tools that can convert the circuit developed by Chisel into the Verilog format, and then modify its design or integrate with other circuits. RISC-V adopts BSD license on the license, instead of GPL license, which is common for open source software. If GPL license is adopted, the results of extended development must also be licensed by GPL, and its source code (the mainland called the original code, Source code), but many companies want to maintain a competitive advantage and regard their own developed programs as trade secrets and do not want to open them. In fact, Android also rewrites the Linux core because of this, so that hardware vendors that adopt the Android operating system do not need to open it. The driver keeps its secrets, and many mobile phone manufacturers support Android. But BSD is different. BSD allows the use of its open results, but the extended software does not need to be open, which is obviously more generous than the GPL authorization. As for the compiler and related software support, there are softwares such as gcc/glibc/GDB, LLVM/Clang, Linux, Yocto, VerificationSuite, etc. Although RISC-V has a good idea, if the actual chip developed does not perform well, it will still be difficult to compete with commercial ISA. For this, the leading academic unit of RISC-V at the University of California, Berkeley (UC Berkeley) has developed a reputation. It is Rocket's RISC-V chip, and it is deliberately selected for comparison with the Arm core (Cortex-A5) implemented by the same process (TSMC 28nm) technology (Figure 2). Figure 2 Comparison of Rocket core and Cortex-A5 technical characteristics. First, compare the clock frequency. Both can reach above 1GHz, which is regarded as a tie; in terms of performance, RISC-VRocket can reach 1.72DMIPS/MHz, which is about 10% higher than ArmCortex-A5; outside of the cache memory, the execution core In terms of the wafer area occupied, RISC-VRocket is only 0.14 square millimeters, which is only half of Cortex-A5. Even if both contain 16KB of cache memory, they are still only 70% of A5. The performance that Rocket can produce per Hz is 1.5 times that of A5; in terms of power consumption, Rocket is about 40% of A5. However, this comparison still has a slightly different footing. Rocket adopts a 64-bit architecture, but RISC-V also has a 32-bit architecture version. If both adopt a 32-bit version or both adopt a 64-bit version , Maybe a more fair comparison. In addition to Rocket, there will also be 8 or 9 implementation cores such as ORCA and PULPino. The aforementioned GAP8 is based on PULPino. In addition to the MCU/CPU core technology, RISC-V is also actively developing the core connection interface circuit technology, namely TileLink. The reason is that Arm also lays out the interface technology and agreements required between the core or between the core and the periphery in addition to the core technology. Therefore, there are AMBA agreement, ASB bus, APB bus, etc., and subsequent expansion and development of AHB, ATB, AXI, ACE, CHI and other interfaces. RISC-V is not the first open project Although RISC-V is an open hardware project that has recently attracted attention, it is not the only or earliest project. There have been OpenRISC, OpenSPARC, etc. before, but this type of project encountered some development restrictions after its launch, and the OpenRISC architecture is old and slow in development. The 64-bit version of the architecture is not mature enough, and OpenSPARC comes from UltraSAPRC, which is gradually losing its price-performance ratio. The community after opening is not active (Figure 3). Figure 3 Comparison of the features of SPARCV8, OpenRISC, and RISC-V. The 64-bit addressing of SPARCv9 is a proprietary technology and is not open. In addition, some projects are too academic and can work theoretically, but when implemented into actual circuits, it is not easy to improve performance, reduce power consumption, reduce wafer area, etc., or some projects are not easy to import existing software assets that other ISAs already have (Driver, sample program, application program, etc.), it is difficult to recompile and rewrite. All of the above, RISC-V has been deliberate at the beginning of its establishment. The definition of the new architecture plan from scratch must be close to commercial implementation, and it is also convenient to guide the software assets of other existing ISAs. Therefore, there have been many semiconductor industries at the beginning of its establishment Large companies participate together and ensure the development of the community. It is worth mentioning that chip vendors with proprietary architectures have changed their attitudes in recent years. They no longer only sell complete chips, but have also begun to imitate Arm’s business model, allowing core chip technologies to be authorized for further development and application. For example, Intel cooperated with TSMC in 2008. Open the x86 core license, allowing other companies to develop their own chips with the x86 architecture, or NVIDIA opened its GPU core license in 2013, etc. However, for this type of license, its ISA patents and subsequent development trends are still dominated by chip vendors, not Jointly participated in the formulation, this derivative business has not been substantially developed so far. Both IoT/AI are applicable to RISC-V An ISA technology ecosystem can be successful, and it must gain advantages in terms of technical characteristics and scale usage. For example, x86ISA has the best price-performance ratio and has been widely adopted from PCs, while Arm has low power consumption and good performance per watt. Therefore, it has been widely adopted on mobile devices such as mobile phones and embedded devices. Therefore, RISC-V also maximizes the applicability of ISA as much as possible. Therefore, 32-bit and 64-bit architectures are formulated at the same time, and the addressing method also widely supports 16/32/64/128-bit addressing. In terms of actual development, all types of applications are indeed under development. The aforementioned GAP8 chip developed by GreenWave is aimed at IoT applications, using TSMC’s 55LP (Low-Power) process, and the target market is similar to ArmCortex-M0~M7. EsperantoTech, which is invested by WD, uses RISC-V to develop artificial intelligence (AI) chips. It is based on a 64-bit architecture and develops ET-Maxion with 16 cores and ET-Minion with 4,096 cores. It is expected to use TSMC. 7nm process. In addition, FPGA chip manufacturer MicroSemi also proposed RV32IM's RISC-V soft core technology, which enables chip developers to use FPGA chips for evaluation and simulation design in the early stage, and if they want to put them into commercial mass production chips in the future, they can avoid the cost of core licensing. In the past, if we adopted Arm's core development, there were concerns about licensing fees and royalties. In addition, some companies have tried to use the RISC-V architecture but adopt the same silicon intellectual property licensing model as Arm, such as the aforementioned SiFive and Andes. SiFive has launched a 32-bit (RV32) E31 core and a 64-bit (RV64) E51 core. , Both adopt 28-nanometer manufacturing process. The former is targeted at the same application market as Cortex-M3 and M4, while the latter is positioned similarly to Cortex-A53. However, E31 and E51 do not support Linux. However, Linux is widely used in the embedded field. For this reason, SiFive also proposed U54/U54-MC (RV64GC) core, which can support Linux (Figure 4). Figure 4 SiFive launched the RISC-V core U54-MC that supports Linux. Andes puts forward the AndeStarv5 architecture (that is based on RISC-V), which includes a 32-bit N25 core and a 64-bit NX25 core, both of which are made using 28-nanometer HPC process, and emphasized that only a few logic gates are needed. Realize, N25 only needs 30,000 logic gates, NX25 is 50,000. The smaller the amount of logic gates, the smaller the wafer area required, which means that chips can be realized and produced at a lower cost. CEVA also has a 32-bit RISC-V ( RV32IMC), and set to be used in the Bluetooth and Wi-Fi transceiver chip. In addition, although it is based on RISC-V, Andes still makes various enhancements to it, such as using custom instructions to reduce the amount of code by 10%, which can reduce the memory requirements of the program; or speed up the real-time processing when an interrupt occurs Speed, more suitable for real-time applications; or to protect the stack, can prevent malfunction or reduce security issues. Strong RISC-V member lineup There have been many reports on the adoption of RISC-V by major manufacturers, but I will only quickly bring them here. For example, NVIDIA’s GeForce graphics processing unit (GPU) has an Eagle (FastLogic CONtroller, Falcon) controller, and the new Falcon will adopt RISC-V. Architecture, Samsung will also be used in its own mobile chip, WD will also be used in a variety of chips. There is no other reason why the above-mentioned companies embrace RISC-V vigorously. These companies purchase or sell a large number of chips. In the past, the adoption of Arm cores had to pay a huge technology fee. If you switch to RISC-V, you will save a lot of money. On the government side, DARPA funds commercial companies to develop aerospace equipment chips based on the RISC-V architecture. The Indian government also vigorously embraces RISC-V; academic institutions have 35 universities joined, including famous universities, such as the Massachusetts Institute of Technology, Princeton University and others (Figure 5). Figure 5 RISC-V Foundation members, membership is divided into two levels: Platinum or Gold, Silver&AuditorMembers The business model has turned into the biggest worry RISC-V seems to be developing smoothly so far, but in fact, there are some hidden worries. First, RISC-V allows adopters to extend and expand the definition instructions by themselves. If they do it separately, it will split the software compatibility and make it lagging behind. The software ecosystem is more difficult to gather forces to develop. The other is the transformation of the business model of new entrepreneurs. Taking the aforementioned SiFive as an example, the original expected business model is based on a free RISC-V architecture, accepting custom commissioned designs from customers, and charging design fees, but then transformed into Charge fees for the cores that have been developed, such as E31 charges 300,000 U.S. dollars, E51 charges 600,000 U.S. dollars (Andes's 64-bit version claims less than 1 million U.S. dollars). SiFive's authorization is still more generous than Arm. 300,000 and 600,000 US dollars are a one-time fee. Arm, in addition to the one-time fee, also charges royalties for each chip, and RISC-V still has the freedom to modify and switch. However, SiFive has turned to the same route as Arm, which also makes people worry about whether it has violated the original intention of RISC-V. In addition, in the past, the development of open source software, in addition to the obstacles of the inactive community, the follow-up development route disputes, or separate development, or still focus on development, but the route gradually deviates from the original intention or commercial value. These may also happen on the RISC-V project. Finally, Taiwanese manufacturers are also highly interested in RISC-V and see this as a new development opportunity. For example, TSMC can obtain more investment from new chip companies; Andes does not stick to its own proprietary core architecture and embraces RISC-V. , Even if the architecture is incompatible, do not give up the new machine; MediaTek (MediaTek, MTK) also joined the RSIC-V Foundation; chip design service provider Faraday also has expectations for new developments.

Welding Generator Set is high efficient power equipment with All in one functions:

. All in one function of Welding and Power Generating.

. Adopt DC welding power source with easy to strike ARC.

. The ARC is stable with less spattered.

. The welding current is continuous and adjustable with more safe and reliable.

. The wide range of welding current makes it adapt to different welding purpose.

. Providing three phase and single phase auxiliary lighting and power supply.

. Full function of silent type.

. Full function of moving type

welding diesel generator,welding generator set,welding genset,welding diesel genset,welding power generator Guangdong Superwatt Power Equipment Co., Ltd , https://www.swtgenset.com